Memory Block Based Scan-BIST Architecture for Application-Dependent FPGA Testing

<u>Keita Ito</u>, Tomokazu Yoneda, Yuta Yamato, Kazumi Hatayama, and Michiko Inoue

NAIST

Nara Institute of Science and Technology

- Ensure in-field reliability of application circuits on FPGA

- Concerns: Delay faults due to transistor aging

- Solution for ASIC: scan-BIST

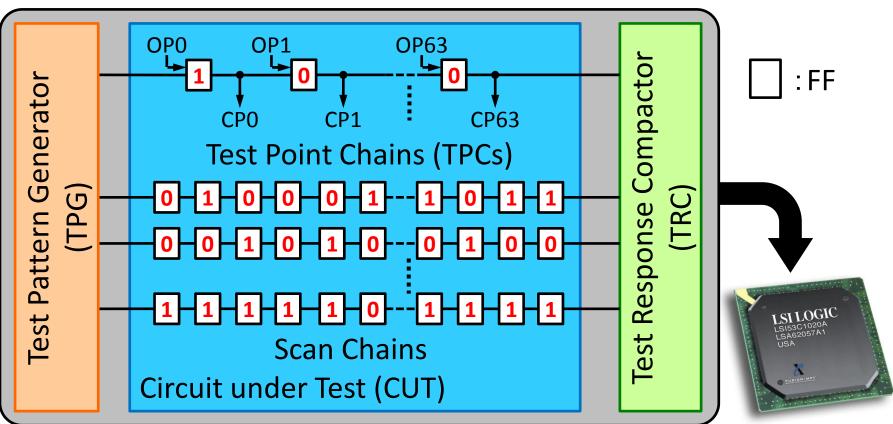

BIST: Built-In Self-Test

- Propose FPGA-specific scan-BIST architecture

- Reduce resource utilization for scan-BIST architecture

- Improve test quality

- Widely used infrastructure for test of ASIC

- Ensure in-field reliability

- Tester circuits are implemented on a VLSI

- Problems of scan-BIST for FPGA testing

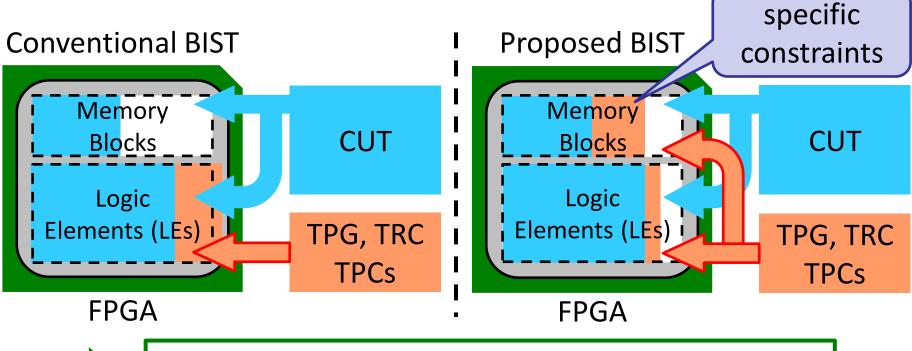

- Target of conventional BIST is ASIC

- FPGA is not a scan-ready device

- Many logic elements (LEs) are required to implement scan chains, TPG, TRC and TPCs

Large Logic Elements overhead

- Challenge

- FPGA-specific scan-BIST architecture

- Area-efficient architecture

Reduce Logic Elements usage

- Memory Block-based BIST Architecture

- Use shift register on memory blocks

- Need to satisfy specific design constraints

Proposed BIST satisfies the constraints

- Proposed BIST can:

- 1. reduce the LE usage by using memory blocks

- 2. achieve higher fault coverage

| Design                          | b17 with<br>scan | Conventional<br>BIST       | Proposed BIST              |                            |

|---------------------------------|------------------|----------------------------|----------------------------|----------------------------|

| Resource for<br>Shift Registers | -                | LEs                        | LEs                        | Memory<br>Blocks           |

| Total LEs                       | 9,334            | 9,493( <mark>+159</mark> ) | 9,911( <mark>+577</mark> ) | 9,550( <mark>+216</mark> ) |

| Total FFs                       | 1,317            | 1,489                      | 1,997                      | 1,333                      |

| Total<br>Memory Bits            | 0                | 0                          | 0                          | 424                        |

| Fault Coverage                  | -                | 49.43 %                    |                            | 54.47 %                    |

- Conventional Technology

- Scan-BIST and Test point insertion

- Proposed Method

- Memory block based scan-BIST architecture

- Test Application Scheme

- Experimental Results

- Achieve higher fault coverage

- Reduce the logic elements usage

- Future Work

Please visit our poster