### Near-Vt RRAM-based FPGA Opportunity for Low-Power Computing

Xifan Tang Pierre-Emmanuel Gaillardon and Giovanni De Micheli

Dec. 12<sup>th</sup>, 2014

International Conference on Field Programmable Technology (ICFPT), Shanghai

# Motivation

### ▲ Challenges

▼Tight power budget

▼Heavy routing architecture

∇Volatility

▲ Key Contributions ▼Study Near-Vt RRAM-based FPGA ▼Size the transistors in RRAM-based FPGA

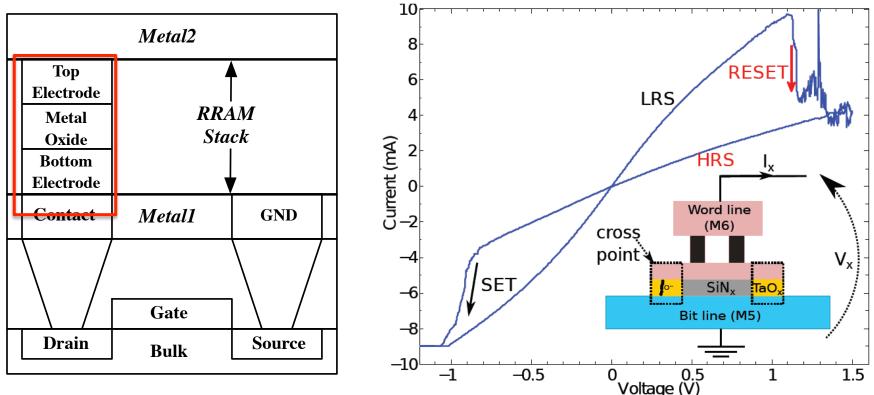

## Resistive Random Access Memory (RRAM)

#### ▲ Non-volatile

#### ▲ Low/High Resistance States(LRS/HRS)

[1] J. Sandrini *et al.*, *Heterogenenous Integration of ReRAM Crossbars in a CMOS Foundry Chip*, Published in 40<sup>th</sup> International Micro and Nano Engineering Conference (MNE).

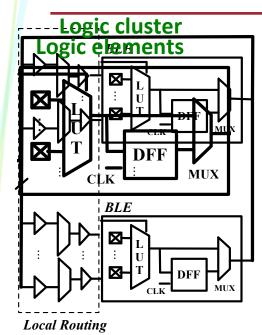

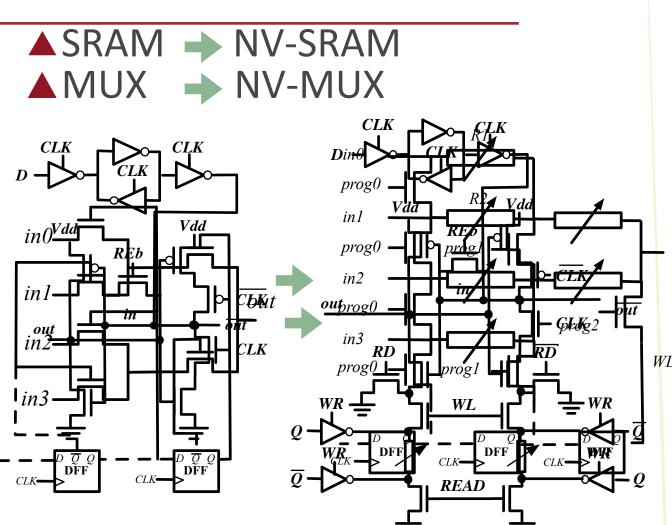

### Part I: Near-Vt RRAM-based FPGA

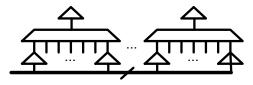

**Connection box**

Switch block

[1] I. Kazi et al., Energy/Reliability Trade-Offs in Low-Voltage ReRAM-Based NdnPvEldtitillangoFlepabeGgASIEEPerCASemrissive6Strneture for Nars-Volucite FPGAs, IEEE/IFIP Int. Conf. on VLSI-SoC, 2012, pp. 94-98.

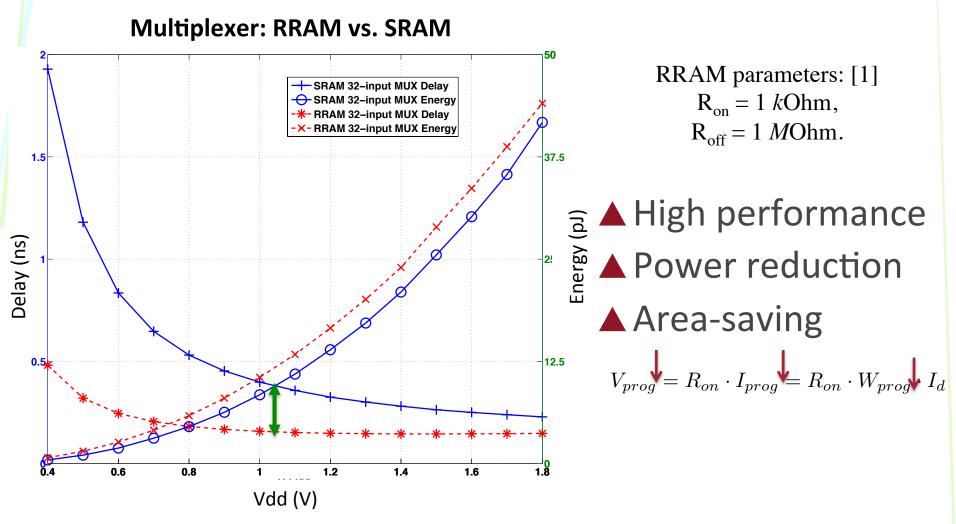

### Impact of Vdd on RRAM Routing Elements

[1] D. Sacchetto et al., Application of Multi-Terminal Memristive Devices: A Review, IEEE CAS Magazine, Vol. 13, No. 2, pp. 23-41.

5

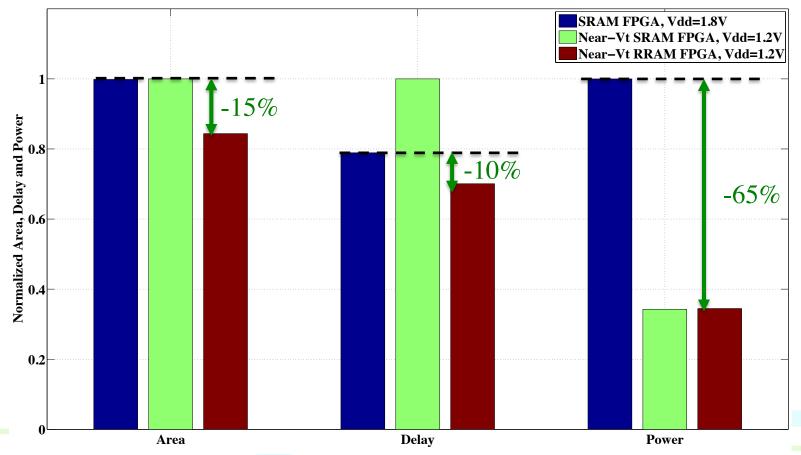

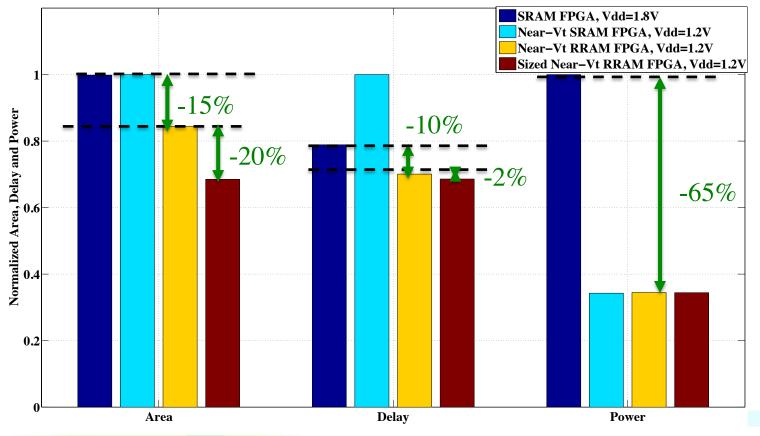

## Near-Vt RRAM-based FPGA

▲ Methodology: VTR flow.

▲ Baseline Architecture: K=6, N=10, I=33, UMC 180nm Technology

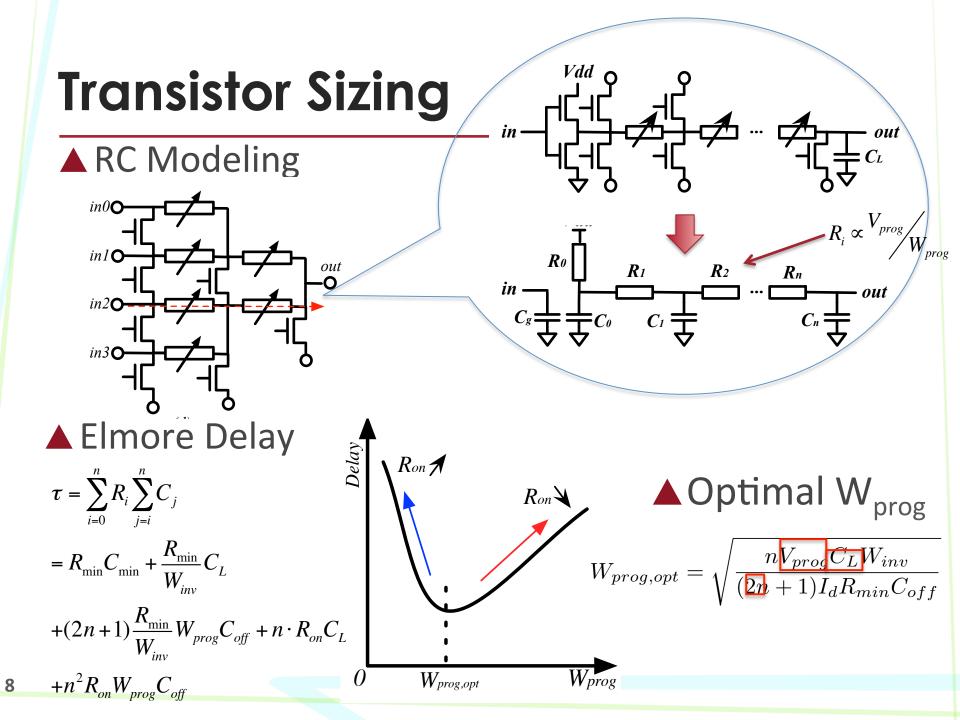

# **Part II: Transistor Sizing**

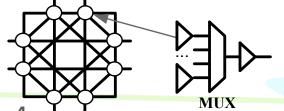

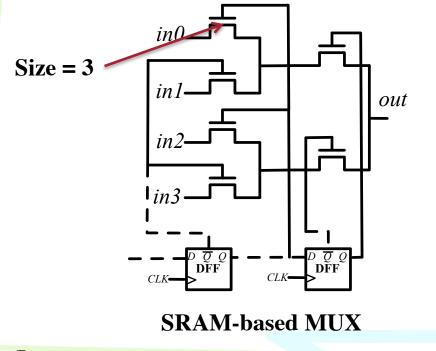

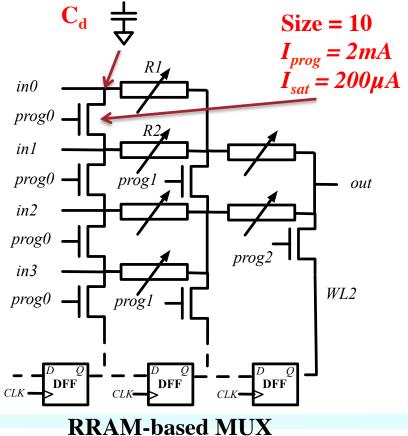

## ▲ Non-negligible programming transistor size ▼Area Overhead

♥Parasitic Capacitance

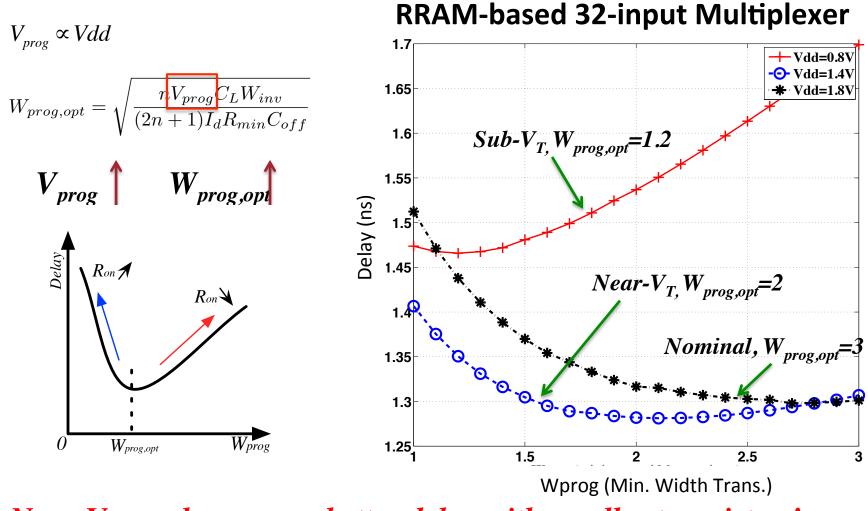

# Impact of Supply Voltage

Near- $V_T$  produces even better delay with smaller transistor !

9

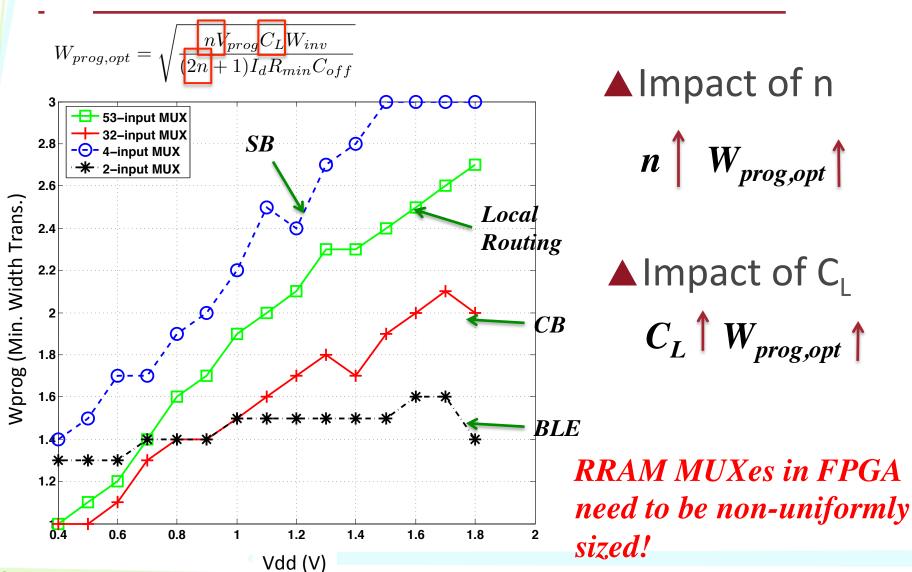

# Study MUXes in FPGA

# Sized Near-Vt RRAM FPGA

▲ Methodology: VTR flow.

▲ Baseline Architecture: K=6, N=10, I=33, UMC 180nm Technology

# Conclusion

▲ Contribution I: Near-Vt RRAM-based FPGA ▽a low-power circuit without performance degradation

▲ Contribution II: Improved area efficiency ▽Non-uniformly sized routing transistors

## Q&A ! Thanks.